---

**CM6530N+CM7104**

**Demo Board User's Guide**

## NOTICES

THIS DOCUMENT IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, DOCUMENT OR SAMPLE.

ALL RIGHTS RESERVED. NO PART OF THIS DOCUMENT MAY BE REPRODUCED OR TRANSMITTED IN ANY FORM OR BY ANY MEANS, ELECTRONIC OR MECHANICAL, INCLUDING INFORMATION STORAGE AND RETRIEVAL SYSTEMS, WITHOUT PERMISSION IN WRITING FROM THE C-MEDIA ELECTRONICS, INC.

## COPYRIGHT

**Copyright© 2010-2023 C-Media Electronics Inc.**

All rights reserved. All content included on this document, such as text, graphics, logos, button icons, images, audio clips, digital downloads, data compilations, and software, is either the exclusive property of C-Media Electronics Inc., its affiliates (collectively, "C-Media"), its content suppliers, or its licensors and protected by Republic of China and international copyright laws.

## TRADEMARKS

C-Media, the C-Media Logo, Xear 3D, Xear 3D Logo, Speaker Shifter, Smart Jack, and Smart Audio Jack, Middleware are trademarks of C-Media Electronics Inc. in Republic of China and other countries. All other brand and product names listed are trademarks or registered trademarks of their respective holders and are hereby recognized as such.

\*C-Media reserves the right to modify the specifications without further notice\*

## **Cmedia Electronics, Inc.**

6F, 100, Sec. 4, Civil Boulevard, Taipei, Taiwan 106, R.O.C.

TEL: 886-2-8773-1100      FAX: 886-2-8773-2211

<http://www.Cmedia.com.tw>

For detailed product information, please contact [sales@cmedia.com.tw](mailto:sales@cmedia.com.tw)

## Revision Notes

| Revision | Date       | Description |

|----------|------------|-------------|

| 1.0      | 2023/04/21 | First draft |

|          |            |             |

|          |            |             |

|          |            |             |

## TABLE OF CONTENTS

|                                                           |        |

|-----------------------------------------------------------|--------|

| NOTICES .....                                             | - 2 -  |

| SECTION 1 OVERVIEW                                        |        |

| 1.1    Introduction .....                                 | - 5 -  |

| 1.2    Demo Board Contents.....                           | - 7 -  |

| 2.1    Board as USB Audio Device.....                     | - 8 -  |

| 2.2    Playback / Recording Functions.....                | - 8 -  |

| 2.2.1    Line Output (J24).....                           | - 8 -  |

| 2.2.2    EARPHONE (J20).....                              | - 9 -  |

| 2.2.3    RCA Output R_ch (J21) & L_ch (J22) .....         | - 9 -  |

| 2.2.4    MIC IN (J6) .....                                | - 9 -  |

| 2.3    Evaluation Board with peripheral Control .....     | - 10 - |

| 2.3.1    HID Buttons (SW2, SW3, SW4, SW5) .....           | - 10 - |

| 2.3.2    Function Switch (SW6) .....                      | - 11 - |

| 2.3.3    EQ Effect Switch (SW1).....                      | - 11 - |

| 2.3.4    TEST Pin (J14) .....                             | - 11 - |

| 2.3.5    UART Interface (J18).....                        | - 12 - |

| 2.3.6    I2C Interface (J4) .....                         | - 12 - |

| 2.3.7    MCLK1 Sel(J9) .....                              | - 13 - |

| 2.3.8    SPDIF & Class D Amp power pin header (J23) ..... | - 13 - |

| 2.3.9    CM7104 Master I2C pin header (J5).....           | - 14 - |

| 2.3.10    LED (D5) & 3 colors LED (D4).....               | - 14 - |

| 2.3.11    EUA Class D Amp.....                            | - 15 - |

| 2.3.12    SPDIF OUT(OPT3) & SPDIF IN(OPT2).....           | - 15 - |

| 2.3.13    Type C VBUS to USB5V (J12) .....                | - 16 - |

| 2.3.14    DMIC1 (J8) & DMIC2 (J11).....                   | - 16 - |

# SECTION 1 OVERVIEW

## 1.1 Introduction

The CM6530N is a low power USB 2.0 audio controller built in 8051 for flexible applications. Accompany with ultra low power codec makes it suitable for low power headset, notebook/mobile docking and microphone applications. The internal 8051 can also be developed to different applications, such as Android Phone or iDevice Accessories with special functions, such as HID buttons or LED control. The CM6530N is compatible with USB Audio Class 1.0 and USB 2.0 full-speed, Thus it can plug and play without additional software installation on the major operation systems. The I2S support 8-96 KHz sampling rate and 16/24bits resolution.

The CM6530N also integrates 512K Bytes flash (including 32KB F/W programming size) but requires few passive components to make a finished product. Thus it can save the total BOM cost and PCB area can be smaller.

The CM7104 is a highly-integrated Audio DSP plus CODEC system whose high-performance and low-power consumption make it ideal for a wide range of mobile systems, such as Tablet, Smartphone and Ultra-book.

The CM7104 DSP core, Tensilica HiFi EP, with extensive memory resources provides low-power advanced digital signal processing. Given that Tensilica HiFi core is widely used by many third-party software developers, it makes CM7104 create an extensive wide software reference design ecosystem, including multi-microphone advanced voice processing (NS, AEC...etc.), low power speech trigger and recognition, and high-quality well-known branding audio post-processing. The CM7104 integrates a fully-flexible digital mixing and routing with asynchronous sample rate converter (ASRC) to support

---

the DSP core for wide use case flexibility.

Two digital audio interfaces are provided, supporting I<sub>2</sub>S/PCM/TDM audio formats. Two differential analog microphone inputs and up to four digital microphone inputs can accept audio signals from multiple microphone or line input sources. Two differential line outputs can provide high performance analog audio signal outputs for connecting high-quality amplification systems.

The CM7104 also combines a variety of low-power fixed-function signal processing components. The advanced multiband DRC (Dynamic Range Control) enables further digital audio processing capabilities on playback or record paths. Advanced DRC function comprises multi-section and multi-band parts, ensuring signal level maintenance, maximizes loudness, and prevents audio clipping and speaker damage.

The CM7104 can be powered from a 1.8V power supply only, and its individual blocks are all design for power efficient target, helping devices to achieve long time playback, record, voice talk...etc. cases. The CM7104 is supplied by a LQFP48 package within 7x7 mm<sup>2</sup>.

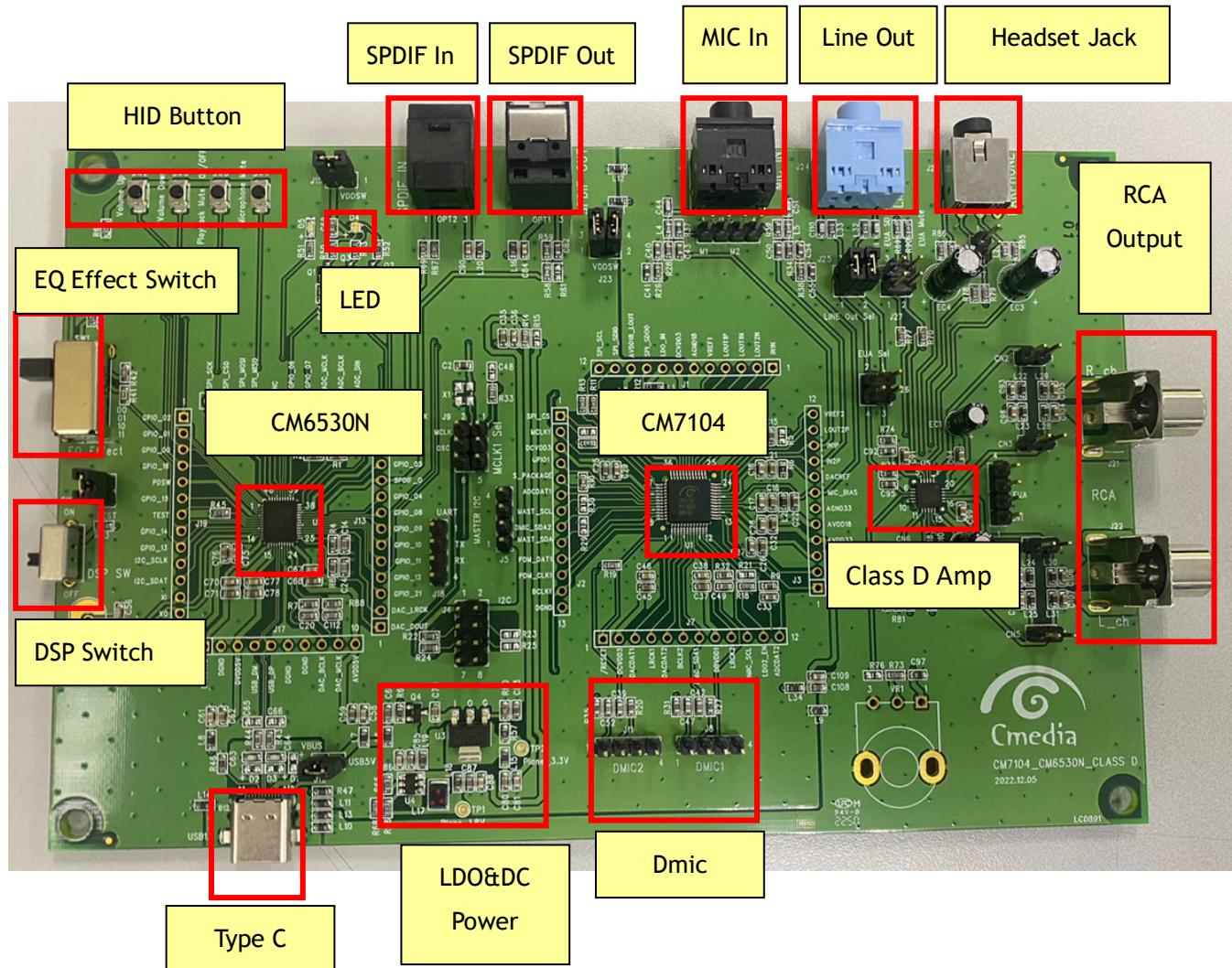

## 1.2 Demo Board Contents

The CM6530N+CM7104 USB Audio controller demo board has several hardware features. With each feature's description in figure, the feature's location can be clearly identified.

## SECTION 2 GETTING STARTED

### 2.1 Board as USB Audio Device

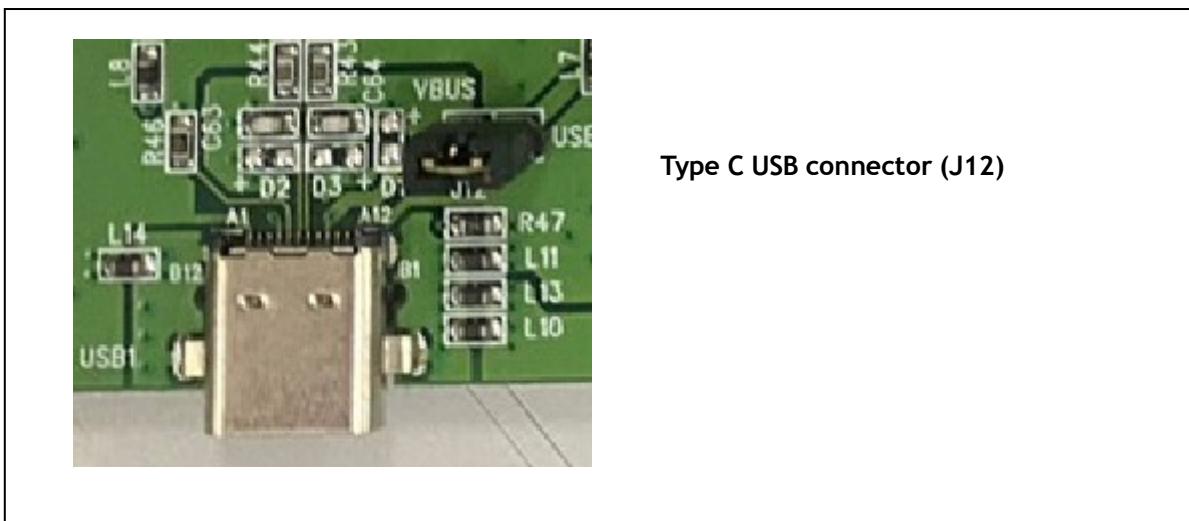

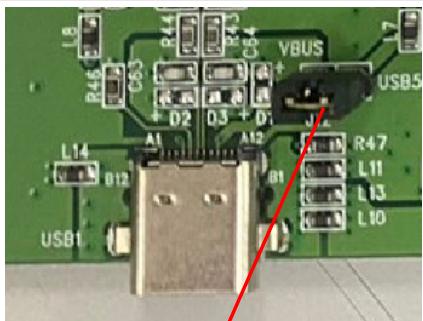

Connect the demo board to the host by plugging the USB core with a type C connector, as shown below.

### 2.2 Playback / Recording Functions

#### 2.2.1 Line Output (J24)

Line Out (J24) (J25 Pin1-3 & Pin 2-4 short)

Output from the CM7104 without the Class D Amp.

| Symbol             | Description               |

|--------------------|---------------------------|

| Connect J25 Pin1-3 | CM7104 audio R_ch output. |

| Connect J25 Pin2-4 | CM7104 audio L_ch output. |

### 2.2.2 EARPHONE (J20)

**EARPHONE(J20)** is output from the class D AMP. Have jack detect function with input.

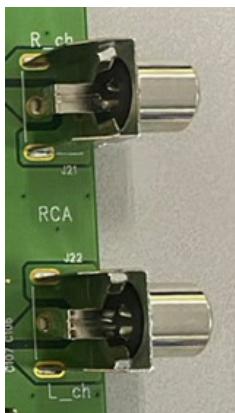

### 2.2.3 RCA Output R\_ch (J21) & L\_ch (J22)

**RCA Output R\_ch (J21) & L\_ch (J22)** from the Class D AMP.

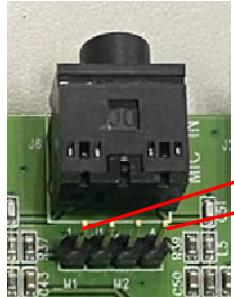

### 2.2.4 MIC IN (J6)

**Stereo MIC input**

J10 header pin 1 MIC IN L\_ch & pin3 MIC IN R\_ch.

## 2.3 Evaluation Board with peripheral Control

CM6530N+CM7104 embedded external peripheral control and functions enable & select pins.

- **HID Buttons**

- **Function Switch**

- **LED Indicators**

- **Test Pin (for flash recover)**

- **GPIO Function Switch Pins**

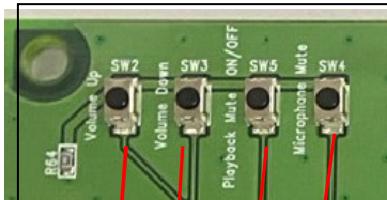

### 2.3.1 HID Buttons (SW2, SW3, SW4, SW5)

| Symbol                                               | Description          |

|------------------------------------------------------|----------------------|

| SW2(GPIO_00)                                         | Volume Up +          |

| SW3(GPIO_01)                                         | Volume Down-         |

| SW5(GPIO_07)                                         | Playback Mute ON/OFF |

| SW4(GPIO_03)                                         | Microphone Mute      |

| All the button functions can be replaced by Firmware |                      |

### 2.3.2 Function Switch (SW6)

Switch the CM7104 DSP ON/OFF by GPIO\_15).

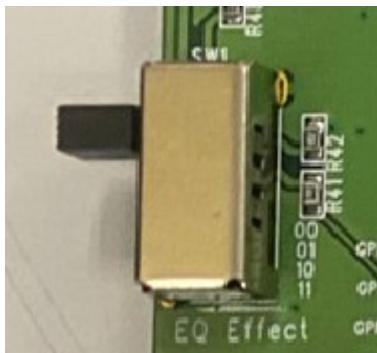

### 2.3.3 EQ Effect Switch (SW1)

Switch the EQ function by GPIO\_12& GPIO\_13).

### 2.3.4 TEST Pin (J14)

| J14  | Description                                                             |

|------|-------------------------------------------------------------------------|

| Test | When firmware crash, short this pin could enable firmware recover mode. |

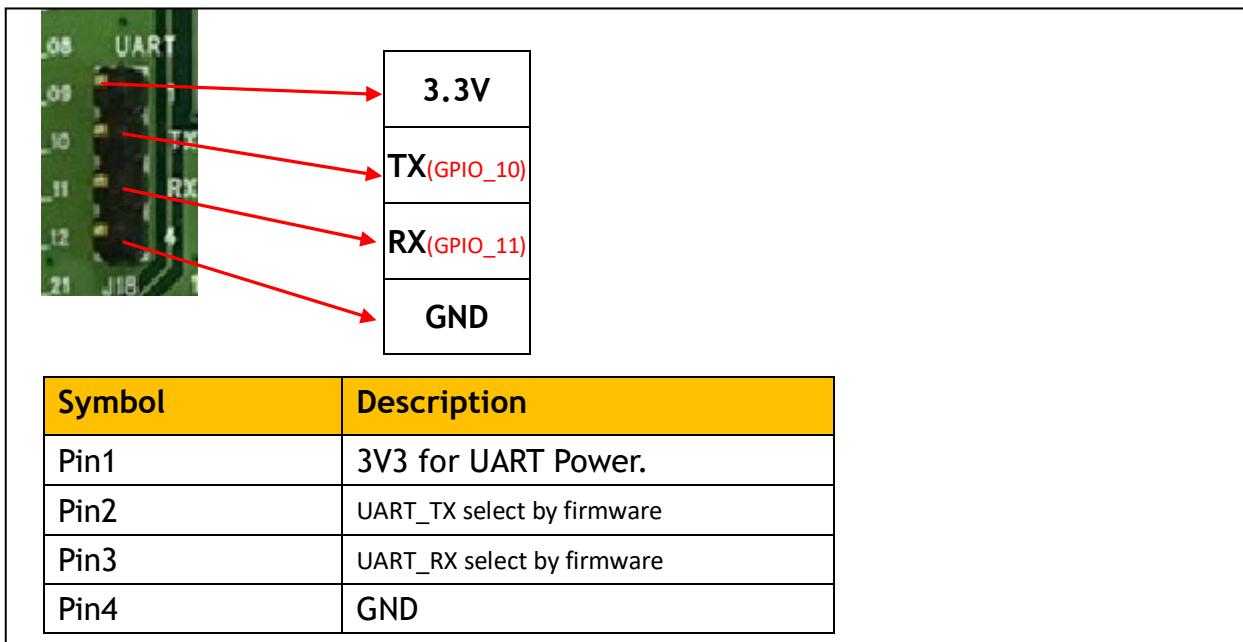

### 2.3.5 UART Interface (J18)

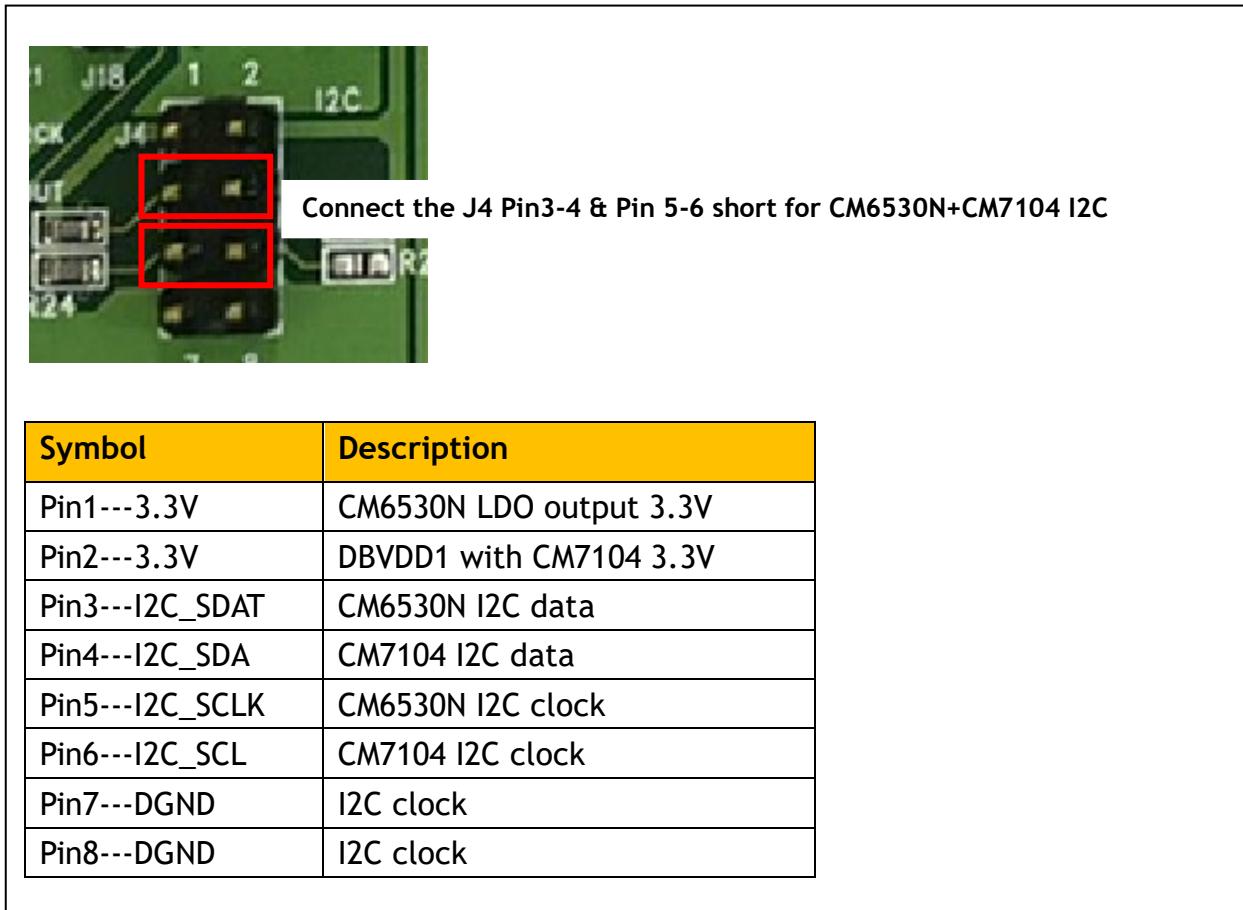

### 2.3.6 I2C Interface (J4)

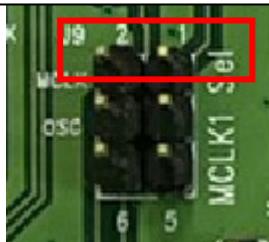

### 2.3.7 MCLK1 Sel(J9)

Connect the J9 Pin1-2 select the DAC\_MCLK clock.

| Symbol            | Description                        |

|-------------------|------------------------------------|

| Connect J9 Pin1-2 | CM7104 MCLK1 from CM6530N DAC_MCLK |

| Connect J9 Pin3-4 | CM7104 MCLK1 from OSC X1           |

| Connect J9 Pin5-6 | CM7104 MCLK1 from CM6530N GPIO_09  |

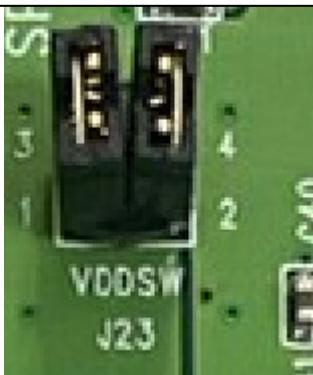

### 2.3.8 SPDIF & Class D Amp power pin header (J23)

| Symbol             | Description                |

|--------------------|----------------------------|

| Connect J23 Pin1-3 | SPDIF 5V power input       |

| Connect J23 Pin2-4 | Class D Amp 5V power input |

### 2.3.9 CM7104 Master I2C pin header (J5)

|               |                                                                                                                                    |     |            |            |      |

|---------------|------------------------------------------------------------------------------------------------------------------------------------|-----|------------|------------|------|

|               | <table border="1"> <tr><td>GND</td></tr> <tr><td>MASTER_SCL</td></tr> <tr><td>MASTER_SDA</td></tr> <tr><td>3.3V</td></tr> </table> | GND | MASTER_SCL | MASTER_SDA | 3.3V |

| GND           |                                                                                                                                    |     |            |            |      |

| MASTER_SCL    |                                                                                                                                    |     |            |            |      |

| MASTER_SDA    |                                                                                                                                    |     |            |            |      |

| 3.3V          |                                                                                                                                    |     |            |            |      |

| <b>Symbol</b> | <b>Description</b>                                                                                                                 |     |            |            |      |

| Pin1          | DBVDD 3.3V                                                                                                                         |     |            |            |      |

| Pin2          | MASTER_SDA data pin                                                                                                                |     |            |            |      |

| Pin3          | MASTER_SCL clock pin                                                                                                               |     |            |            |      |

| Pin4          | GND                                                                                                                                |     |            |            |      |

### 2.3.10 LED (D5) & 3 colors LED (D4)

|                  |                                       |

|------------------|---------------------------------------|

|                  | Pin header J15 is LED 5V power input. |

| <b>Symbol</b>    | <b>Description</b>                    |

| Function LED(D4) | Function indicator                    |

| Function LED(D5) | DSP algorithm On/Off indicator        |

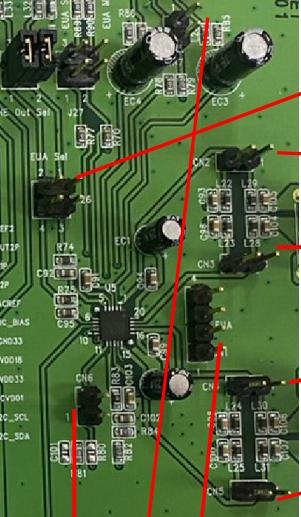

### 2.3.11 EUA Class D Amp

|                                                                                                                              |                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| EUA Sel(J26) pin2 audio L-ch, pin1 R-ch.<br><b>CN2 EUA_RN</b><br><b>CN3 EUA_RP</b><br><b>CN4 EUA_LP</b><br><b>CN5 EUA_LN</b> |                                                                                          |

| <b>Symbol</b>                                                                                                                | <b>Description</b>                                                                       |

| EUA Sel(J26)                                                                                                                 | Connect J26 Pin1-3/Connect J26 Pin2-4                                                    |

| CN1                                                                                                                          | EUA output pin header                                                                    |

| CN6                                                                                                                          | Floating is disable AGC function, provides the 64 steps AGC (Auto Gain Control) function |

| CN7                                                                                                                          | Output mode control input, high for SE output mode and low for BTL mode.                 |

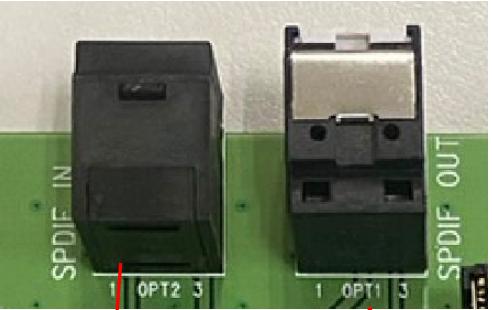

### 2.3.12 SPDIF OUT(OPT3) & SPDIF IN(OPT2)

|                                             |  |                         |

|---------------------------------------------|--|-------------------------|

| <b>Symbol</b><br><b>OPT2</b><br><b>OPT3</b> |  | <b>Description</b>      |

|                                             |  | SPDIF output connector. |

|                                             |  | SPDIF input connector.  |

### 2.3.13 Type C VBUS to USB5V (J12)

| Symbol | Description                         |

|--------|-------------------------------------|

| J12    | Connect J12 pin1-2 for system USB5V |

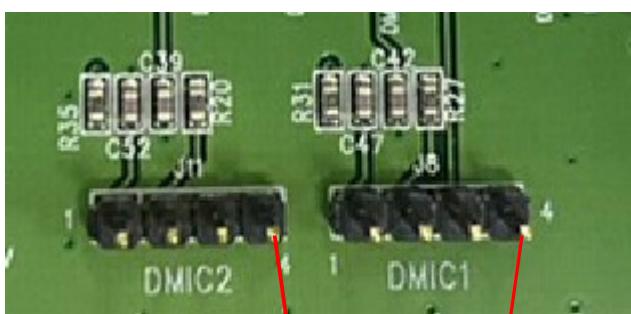

### 2.3.14 DMIC1 (J8) & DMIC2 (J11)

| Symbol           | Description               |

|------------------|---------------------------|

| DMIC1 (J8) Pin1  | DBVDD 3.3V for DMIC power |

| DMIC1 (J8) Pin2  | DMIC data1 input          |

| DMIC1 (J8) Pin3  | DMIC clock output         |

| DMIC1 (J8) Pin4  | Digital GND               |

| DMIC2 (J11) Pin1 | DBVDD 3.3V for DMIC power |

| DMIC2 (J11) Pin2 | DMIC Data2 input          |

| DMIC2 (J11) Pin3 | DMIC clock output         |

| DMIC2 (J11) Pin4 | Digital GND               |